Jean-François Lucas 03/12/09 Page(1

# Introduction au séquentiel

# La boucle cybernétique

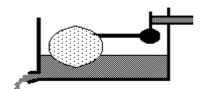

Partons de la boucle cybernétique classique, en voici une application : Le régulateur de niveau d'eau.

# La boucle cybernétique avec réaction positive

Regardons maintenant la boucle cybernétique avec une réaction positive. Elle est illustrée plus concrètement par le montage ci-dessous.

En fait il présente deux états stables :

- Soit le niveau baisse, le flotteur descend et l'eau n'arrive plus.

- Soit le niveau monte, le flotteur monte et l'eau arrive à plein débit.

Le montage est bistable.

# Introduction: Faire intervenir la dimension temps

Ainsi on introduit la dimension temporelle : Le temps et ce montage se comportent comme des mémoire : On débouche sur la notion de mémoire.

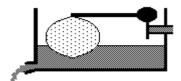

### Le dièdre

Le dièdre obtus, dessiné au-dessus constitue un autre exemple de réalisation physique du bistable. L'état A est instable, et les deux états B et C sont stables.

Jean-François Lucas 03/12/09 Page(2

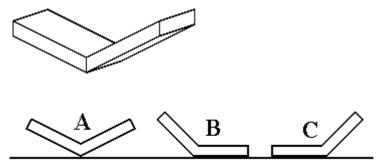

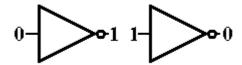

### Suiveur et inverseur

Avant de continuer, faisons un rappel sur deux circuits électroniques très simples.

#### Suiveur

Comme son nom l'indique il suit ce qu'on lui dit :

Si on lui dit 1 il répète 1.

Si on lui dit 0 il répète 0.

#### Inverseur

Comme son nom l'indique il inverse ce qu'on lui dit :

Si on lui dit 1 il répond 0.

Si on lui dit 0 il répond 1.

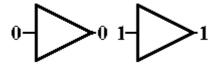

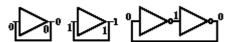

## Le bistable

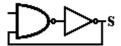

Le bistable peut facilement s'implémenter électriquement avec un suiveur à qui on met un réaction positive : On ramène la sortie sur l'entrée.

Ci-dessus, la figure de gauche, monte l'état stable à 0, celle du centre l'état stable à 1.

Le bistable peut aussi s'implémenter avec deux inverseurs (figure de droite).

# Le forçage du bistable

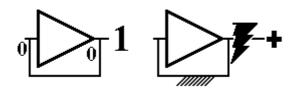

### Forçage violent du bistable

On sait que ce bistable demeure dans un état stable tant qu'il n'est pas perturbé : C'est le principe de fonctionnement d'une mémoire. Mais vient le moment où on veut réécrire le contenu de la mémoire, où l'on veut forcer un bistable dans un autre état.

Quand je veux forcer un niveau 1 sur un bistable à l'état zéro, au niveau électrique, c'est comme si je connecte une masse à une tension positive. Ca s'appelle un court-circuit. Même s'il ne dure que le temps de basculement du circuit, on va chercher à l'éviter.

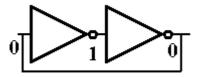

# Forçage anodin du bistable

#### Implémentation:

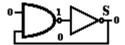

Pour forcer sans danger un bistable, on utilise un bistable crée avec deux inverseur :

Ensuite, on remplace l'inverseur de gauche par un NON ET.

### Fonctionnement d'un forçage à 0

On sait que le moindre 0 en entrée d'un ET donne un 0 en sortie. Donc le moindre 0 en entrée d'un NON ET donne un 1 sur sa sortie. Il est ensuite inversé, et on obtient un 0 en sortie du montage, qui revient en entrée confirmer le 0 que nous mettons. Ce qui est devenu inutile. Quand nous relâchons notre effort le système ne bouge pas, il est devenu stable.

#### Fonctionnement d'un forçage à 1

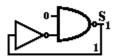

Pour disposer d'un circuit qui se force facilement à 0, il faut remplacer l'inverseur de droite par un NON ET.

Un 0 sur son entrée force un 1 en sortie. Ce dernier revient en entrée, est inversé par le circuit de gauche qui fournit un 0 qui vient confirmer le forçage, qui peut cesser. Le système est stabilisé à 1.

#### Schéma final

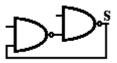

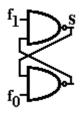

Finalement si on veut un bistable qui puisse être forcé à 0 et à 1, on panache les deux solutions partielles et on obtient finalement le schéma suivant :

Cette représentation se rapproche plus de notre explication, mais souvent on préfère celle ci-dessous, mais il faut bien voir qu'elles sont équivalentes.

# Quelques remarques:

- Notez bien que les f<sub>i</sub> sont des entrées de forçage ; f<sub>0</sub> force la sortie à 0 et f<sub>1</sub>, à 1.

- Au repos, i.e. en mémorisation, les entrées doivent être maintenues à 1.

- Il faut forcer soit f<sub>0</sub> soit f<sub>1</sub>, mais pas les deux entrées ensemble.

### Synoptique de la Bascule RS

Dans le synoptique américain de la RS:

- L'entrée f<sub>0</sub> (de forçage à 0) se nomme R (comme Reset : Remise à zéro).

- L'entrée  $f_1$  (de forçage à 1) se nomme S (comme Set : Forçage à 1).

- La sortie s'appelle Q.

## Chargement d'un bistable avec la bascule DT

Il faut bien voir que les entrées  $f_i$  permettent de forcer un niveau en sortie en évitant de court-circuiter le montage, mais il faut encore une intervention humaine externe pour mémoriser un bit dans ce bistable.

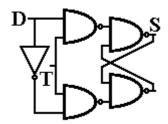

#### Présentation de la bascule DT

Elle permet de mémoriser un bit dans un bistable seulement au moyen de signaux électriques.

### Fonctionnement de la bascule DT

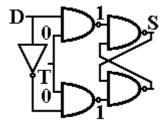

#### Fonctionnement de la DT en mémorisation

Quand l'entrée T est à 0, Le bistable qui est derrière les deux NON ET voit ses deux entrées de forçage à 1. Elle est donc au repos.

#### Chargement de la DT

Pendant que l'on présente l'information à mémoriser (1) sur l'entrée D, il faut donner une impulsion sur l'entrée T, les deux NON ET sont donc dans un état différent et forcent le bistable qui est derrière à l'état 1.

Jean-François Lucas 03/12/09 Page(5

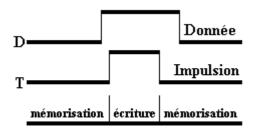

## Chronogramme

Il faut que l'impulsion d'écriture disparaisse avant que l'entrée D ne bouge et l'information fournie par cette dernière est mémorisée.

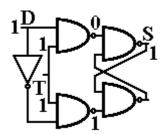

# Synoptique de la Bascule DT

Dans le synoptique américain de la DT :

- L'entrée D de la donnée à mémoriser, se nomme D (comme Data : Donnée).

- L'entrée T (de l'impulsion d'écriture) se nomme T (comme Time : Le temps).

- La sortie s'appelle Q.

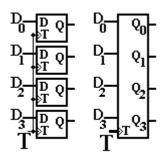

# Fabriquer un registre de N bits

On peut regrouper N bascules DT en parallèle, présenter 4 bits de données sur leur entrée Q, et relier leur entrée T. Ainsi elles se chargeront toutes au même moment.

Finalement, on obtient un registre de N bits. Il servira de tampon (Buffer) ou d'accumulateur (Dans l'Unité Arithmétique et Logique).